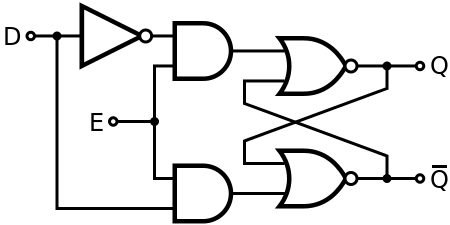

Characteristics Table for the Toggle Function CLK Thus the Q output of the flip-flop “toggles” at each positive going edge (for this example) of the CLK pulse. The negative transistion of the CLK pulse at time t 4 from HIGH to LOW once again has no effect on the output. The negative transistion of the clock pulse from HIGH to LOW at time t 2 has no effect on the output at Q as the flip-flop is reset into one stable state.Īt the next rising edge of the clock signal at time t 3, the logic “1” at T passes to Q, changing its state making output Q HIGH again. At the rising edge (assuming positive transistion) of a CLK pulse at time t 1, the output at Q changes state and becomes LOW, making Q HIGH. Now let’s suppose that input T is HIGH (T = 1) and CLK is LOW (CLK = 0). Thus the output remains unchanged when T = 0. At the rising edge or falling edge of a CLK pulse, the logic “0” condition present at T prevents the output at Q from changing state. Suppose that initially CLK and input T are both LOW (CLK = T = 0), and that output Q is HIGH (Q = 1). The toggle or T-type flip-flop gets its name from the fact that its two outputs Q and Q invert from their previous state as it toggles back and forth every time it is triggered (T = 1). While the Data (D) flip-flop is a variation of a clocked SR flip-flop constructed using either NAND or NOR gates, the Toggle (T) flip-flop is a variation of the clocked JK flip-flop. So JK flip-flops are not built using the basic NAND or NOR gate configurations as shown but instead are constructed to form more advanced master-slave (edge-triggered) flip-flops which are more stable.

But as the outputs are fed back, the outputs will change state continuously after being complemented once, causing the output at Q to oscillate between set and reset. The problem here is that if both the J and K data inputs are at logic “1”, HIGH at the same time (J = K = 1), when the clock (CLK) input goes HIGH, its outputs switch and change state complementing each other.

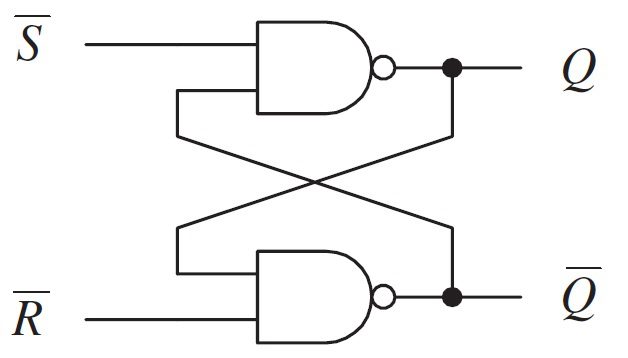

Where: Q represents the present steady state of the flip-flop and Q+1 is the next switching state. Then we can define this switching action in Boolean form as being: Where: X means “don’t care”, a “0” or a “1”, and _↑¯ is the positive rising-edge of the clock pulse. Basic JK Flip-flop Circuit using NAND Gates But before we look at T-type flip-flops in more detail, let’s first remind ourselves of the basic JK flip-flop circuit and switching action. The JK Flip-flop can be classed as a “universal” flip-flop because it can be configured and used to replicate the switching action of other types of flip-flops depending on the logical states applied to its J and K inputs. We remember from our previous tutorial that the JK flip-flop is an asynchronous flip-flop where its input condition (HIGH or LOW), and its present steady state, both determine its next switching state. Toggle flip-flops, TFF’s or simply “T-type flip-flops” are not available commercially as a dedicated TTL or CMOS logic chip, they can be easily constructed by connecting together the J and K inputs of a basic JK flip-flop where the J input behaves like a Set (S) command, and the K input behaves like a Reset (R) command. Toggle flip-flops have a single input and one or two complementary outputs of Q and Q which change state on the positive edge (rising edge) or negative edge (falling edge) of an input clock signal or pulse. The toggle flip-flop can be used as a basic digital element for storing one bit of information, as a divide-by-two divider or as a counter. The Toggle Flip-flop is another type of bistable sequential logic circuit based around the previous clocked JK flip-flop circuit.

0 kommentar(er)

0 kommentar(er)